prbs checker|PolarFire® FPGA and PolarFire SoC FPGA Transceiver : Cebu PRBS pattern checker The scrambling seed in the pattern checker is self-synchronized when the JESD204C IP achieves deskew alignment. The pattern checker requires 8 . Want to discover art related to megaman11? Check out amazing megaman11 artwork on DeviantArt. Get inspired by our community of talented artists.

PH0 · verilog

PH1 · Verifying Link and Transceivers using Pseudo Random Binary

PH2 · Pseudorandom binary sequence

PH3 · PolarFire® FPGA and PolarFire SoC FPGA Transceiver

PH4 · A Low Power 28 Gb/s 2 PRBS Generator and Check with

PH5 · 5.2.2.6.1. PRBS Checker

PH6 · 4.3 PRBS7 Checker

PH7 · 3.1.5. Pattern Generator and Checker

Rise of The Republic is the newest DLC for Total War: ROME 2. In this video, Jordan will guide you through the perks and traits of each of the new factions a.

prbs checker*******PRBS Checker. You can use Cyclone 10 GX pseudo-random bit stream (PRBS) checker to easily characterize high-speed links without developing or fully implementing any .

Enabling the PRBS Data Checker in non bonded design 6.16.1.4. Enabling the PRBS Checker in bonded designs 6.16.1.5. Disabling/Enabling PRBS Pattern Inversion. .

A pseudorandom binary sequence (PRBS), pseudorandom binary code or pseudorandom bitstream is a binary sequence that, while generated with a deterministic algorithm, is difficult to predict and exhibits statistical behavior similar to a truly random sequence. PRBS generators are used in telecommunication, such as in analog-to-information conversion, but also in encryption, simulation, correlation technique and time-of-flight spectroscopy. The most common example is the

Learn how to use the PRBS7 checker to verify PRBS sequences in RTG4 FPGA SerDes EPCS protocol design. The checker detects and counts errors in the received PRBS .Learn how to use the PRBS7 checker to verify PRBS sequences in RTG4 FPGA SerDes EPCS protocol design. The checker detects and counts errors in the received PRBS .PRBS pattern checker The scrambling seed in the pattern checker is self-synchronized when the JESD204C IP achieves deskew alignment. The pattern checker requires 8 .

[PRBS,seed] = prbs(O,N,seed) calculates a pseudorandom binary sequence and the seed needed to continue the sequence using the seed value.prbs checkerFibonacci is generally used for linear-feedback shift registers (LFSR) for pseudorandom binary sequence (PRBS) generators, scramblers, and descrambers, while Galois is .

Each transceiver has embedded blocks with a built-in PRBS generator and checker that can be used to perform link testing and diagnostics. These test capabilities are available .

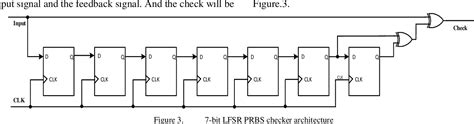

The Pseudo Random Binary Sequence (PRBS) test is a standard feature to verify link quality and transceiver operation. There are two possible diagnostic scenarios: .The PRBS checker is similar to the generator, it eliminate the feedback and do xor operation between the input signal and the feedback signal. And the check will be zero if .

for linear-feedback shift registers (LFSR) for pseudorandom binary sequence (PRBS) generators, scramblers, and descrambers, while Galois is generally used for cyclic redundancy check generators and checkers.Enabling the PRBS Data Checker in non bonded design 6.16.1.4. Enabling the PRBS Checker in bonded designs 6.16.1.5. Disabling/Enabling PRBS Pattern Inversion. 6.16.1.1. Enabling the PRBS Data Generator in non bonded designs x. 6.16.1.1.1. Examples of Enabling the PRBS9 and PRBS31 Pattern Generators in non bonded designs

Guidelines to perform Unidirectional Diagnostics. Enable the transmission of pseudo-random binary sequence pattern on one end of the link (TX), and enable monitoring on the other

PRBS = prbs(O,N,seed,reverse) uses the reverse linear-feedback shift register (LFSR) tap positions and returns a pseudorandom binary sequence pattern that is essentially the same as running the LFSR backward in time. time. Examples. collapse all. Create PRBS Pattern of Order 4. Open Live Script .The PRBS7 checker checks for valid PRBS sequences. If the received sequence does not match with the one transmitted by the generator, the checker indicates an error .PRBS验证器具有下列可供FPGA架构使用的控制和状态信号: rx_prbs_done—指示PRBS序列已完成一个完整周期。在使用rx_prbs_err_clr进行复位前一直保持高电平。 rx_prbs_err—如果发生错误则变为高电平。此信号进行了脉冲扩展,以便能够在RX FPGA CLK域中采集到。PolarFire® FPGA and PolarFire SoC FPGA Transceiver Connect a single fibre from TX to RX of a single port. Connecting TX directly to RX on the line side allows use of the PRBS checker and generator in the one port.Philippine National Police - PRBS PNPprbs checker PolarFire® FPGA and PolarFire SoC FPGA TransceiverA PRBS data generator and checker using discrete-logical devices are presented as an example. Due to the discrete-logical components used, special device-interconnection techniques must be used to reduce the signal-integrity problems and optimize the device interconnection for optimal system performance.Loading application. | Technical Information PortalThe PRBS checker compares the incoming 66b to a newly created 66b PRBS based on the previous data received. To increase robustness to error, the PRBS checker, once in lock, uses a reference PRBS and compare incoming data with this free-running generated reference PRBS. This reference PRBS is synced with the incoming data if there are less .PRBS Signal Generator and Checker. Overview News Downloads Bugtracker. Project maintainers. Soon Chong, Lai; Details. Name: prbs_suite Created: Apr 15, 2011 Updated: Dec 3, 2011 SVN Updated: Jul 18, 2011 SVN: Browse Latest version: download (might take a bit to start.) Statistics: View Bugs: 0 reported / 0 solved.

The PRBS generator, which consumes 1.32 W, uses a high speed 4:1 multiplexer to produce the final output from four quarter-rate streams. The automatic synchronizing PRBS checker consumes 1.2 W and uses a half-rate architecture, demultiplexing the full-rate data stream to lower rate streams that are checked in parallel. PRBS Signal Generator And Checker Home; IC Design Center; Testing / Verification; PRBS Signal Generator And Checker; PRBS Signal Generator And Checker Details Category: Testing / Verification. Created: April 15, 2011. Updated: January 27, 2020. Language: Verilog. Other project properties .user@host2> test interface interface-name prbs-test-stop direction 1 user@host1> test interface interface-name prbs-test-stop direction 0 例如: 要在 RX 处停止 PRBS: user@host2> test interface et-1/1/4 prbs-test-stop direction 1 通过执行以下命令验证 TX 的统计信息: show interfaces et-0/1/2 prbs-stats PRBS Statistics : DisabledIn this paper, a multi-pattern parallel PRBS generator and a dedicated parallel BER tester is proposed for the 8-Gbps On-chip interconnection testing. A unique full-parallel PRBS checker is also proposed. The proposed design, together with the custom-designed high-speed parallel-to-serial and the serial-to-parallel circuit, will be used to test .Pseudo-Random Binary Sequence. Contribute to mgwang37/PRBS development by creating an account on GitHub.

Time difference between China and Perth including per hour local time conversion table. World Time Zone Map. Time Converter. China to Perth. 24 timezones tz. e.g. India, London, Japan. World Time. . Time Difference Calculator Popular Converters . New York vs London Central vs Eastern Time California vs Hawaii Eastern vs Pacific Time. Maps.

prbs checker|PolarFire® FPGA and PolarFire SoC FPGA Transceiver